ENCODERS

1. TUJUAN

-Dapat mengetahui Teori dan Prinsip Kerja dari Encoder

-Dapat membuat dan mensimulasikan Tugas Sistem Digital berupa rangkaian Encoder

2. ALAT DAN BAHAN

a. Multiplexer 8 input

Multiplexer adalah suatu alat atau komponen elektronika yang digunakan untuk memilih 2 sampai banyak input atau masukan untuk diteruskan ke bagian output atau keluaran.

b. Logicstate

Gerbang Logika (Logic Gates) adalah sebuah entitas untuk melakukan pengolahan input-input yang berupa bilangan biner (hanya terdapat 2 kode bilangan biner yaitu, angka 1 dan 0) dengan menggunakan Teori Matematika Boolean sehingga dihasilkan sebuah sinyal output yang dapat digunakan untuk proses berikutnya.

c. Logicprobe

Probe logika adalah probe uji genggam berbiaya rendah yang digunakan untuk menganalisis dan memecahkan masalah status logis dari rangkaian digital. Ketika banyak sinyal perlu diamati atau direkam secara bersamaan, penganalisis logika digunakan sebagai gantinya.

Digunakan untuk menghambat arus agar tidak terlalu besar.

Cara membaca resistor :

e. LED

Sebagai indikator.

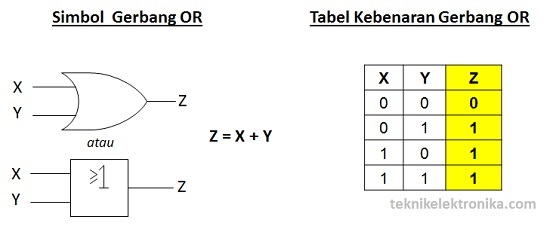

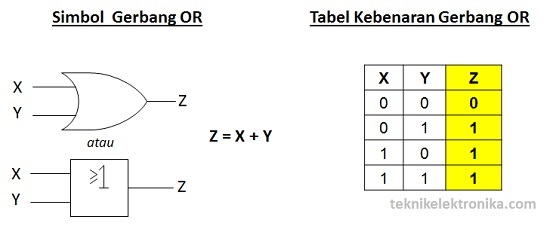

f. Gerbang Logika OR

Gerbang OR memerlukan 2 atau lebih Masukan (Input) untuk menghasilkan hanya 1 Keluaran (Output). Gerbang OR akan menghasilkan Keluaran (Output) 1 jika salah satu dari Masukan (Input) bernilai Logika 1 dan jika ingin menghasilkan Keluaran (Output) Logika 0, maka semua Masukan (Input) harus bernilai Logika 0.

Simbol yang menandakan Operasi Logika OR adalah tanda Plus (“+”). Contohnya : Z = X + Y.

Simbol dan Tabel Kebenaran Gerbang OR (OR Gate) :

g. Inverter

Inverter adalah suatu rangkaian atau perangkat elektronika yang dapat mengubah arus listrik searah (DC) ke arus listrik bolak-balik (AC) pada tegangan dan frekuensi yang dibutuhkan sesuai dengan perancangan rangkaiannya.

h. Encoder 10 input dan 4 output

Encoder adalah rangkaian kombinasional yang mana merupakan operasi kebalikan dari Decoder. Encoder memiliki maksimum 2

n jalur input dimana "n" adalah jalur output. Karena mengkode informasi dari input 2

n menjadi kode n-bit. Encoder akan menghasilkan kode biner yang setara dengan input yang mana adalah "Aktif Tinggi". Oleh karena itu, encoder mengkodekan 2

n jalur input dengan ‘n’ bit.

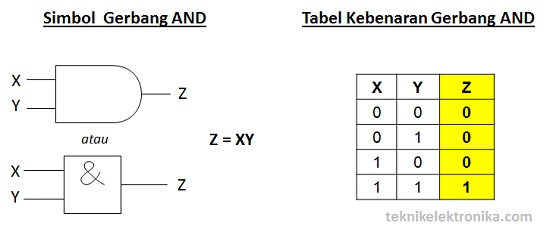

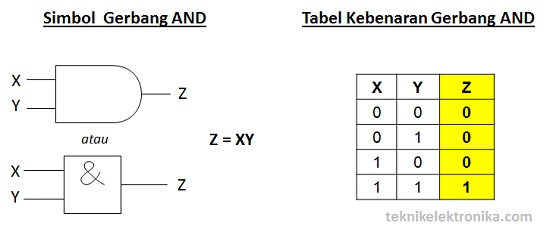

i. Gerbang Logika AND

Gerbang AND memerlukan 2 atau lebih Masukan (Input) untuk menghasilkan hanya 1 Keluaran (Output). Gerbang AND akan menghasilkan Keluaran (Output) Logika 1 jika semua masukan (Input) bernilai Logika 1 dan akan menghasilkan Keluaran (Output) Logika 0 jika salah satu dari masukan (Input) bernilai Logika 0. Simbol yang menandakan Operasi Gerbang Logika AND adalah tanda titik (“.”) atau tidak memakai tanda sama sekali. Contohnya : Z = X.Y atau Z = XY.

Simbol dan Tabel Kebenaran Gerbang AND (AND Gate)

3. DASAR TEORI

Encoder adalah multiplexer tanpa jalur keluaran tunggal. Ini adalah fungsi logika kombinasional yang memiliki 2n (atau lebih sedikit) jalur input dan n jalur output, yang sesuai dengan n jalur pemilihan dalam multiplekser. N jalur keluaran menghasilkan kode biner untuk kemungkinan jalur masukan 2n. Dalam tabel kebenaran, D0 hingga D7 mewakili digit oktal 0 hingga 7. A, B, dan C mewakili digit biner.

Gambar 8.14

Delapan baris masukan akan memiliki 28 = 256 kemungkinan kombinasi. Namun, dalam kasus encoder oktal-ke-biner, hanya delapan dari 256 kombinasi ini yang memiliki arti. Kombinasi variabel masukan yang tersisa adalah kombinasi masukan 'dont' care'. Selain itu, hanya satu baris masukan pada satu waktu yang berstatus logika '1'. Gambar 8.15 menunjukkan implementasi perangkat keras dari oktal-ke-biner encoder dijelaskan oleh tabel kebenaran pada Tabel 8.8. Rangkaian ini memiliki kekurangan yaitu menghasilkan semua urutan keluaran 0 ketika semua jalur masukan berada dalam keadaan logika '0'. Ini dapat diatasi dengan memiliki baris tambahan untuk menunjukkan urutan input semua 0s.

Encoder prioritas adalah bentuk praktis dari pembuat enkode. Pembuat enkode yang tersedia dalam bentuk IC adalah semua pembuat enkode prioritas. Dalam jenis pembuat enkode ini, sebuah prioritas ditetapkan ke setiap masukan sehingga, bila lebih dari satu masukan aktif secara bersamaan, masukan dengan prioritas tertinggi akan dienkode. Kami akan mengilustrasikan konsep pengkodean prioritas dengan bantuan sebuah contoh. Mari kita asumsikan bahwa encoder oktal ke biner yang dijelaskan di paragraf sebelumnya memiliki prioritas input untuk digit orde tinggi.

Gambar 8.15

Asumsikan bahwa input baris D2, D4 dan D7 semuanya secara bersamaan dalam status logika '1'. Dalam hal ini, hanya D7 yang akan dikodekan dan keluarannya akan menjadi 111. Tabel kebenaran dari encoder prioritas tersebut kemudian akan dimodifikasi seperti yang ditunjukkan pada Tabel 8.9. Melihat baris terakhir dari tabel, ini menyiratkan bahwa, jika D7 = 1, maka, terlepas dari status logika dari masukan lainnya, keluarannya adalah 111 karena D7 hanya akan dikodekan. Sebagai contoh lain, Gambar 8.16 menunjukkan simbol logika dan tabel kebenaran dari pembuat enkode BCD desimal 10 baris hingga empat baris yang menyediakan pengkodean prioritas untuk digit orde tinggi, dengan digit 9 memiliki prioritas tertinggi. Dalam tabel fungsional yang ditunjukkan, baris masukan dengan prioritas tertinggi yang memiliki RENDAH di atasnya dikodekan terlepas dari status logika dari baris masukan lainnya.

Tabel 8.8

Gambar 8.16

Tabel 8.9

Beberapa encoder yang tersedia dalam bentuk IC memberikan masukan dan keluaran tambahan untuk memungkinkan perluasan. IC 74148, yang merupakan pembuat enkode prioritas delapan baris hingga tiga baris, adalah contohnya. ENABLE-IN (EI) dan terminal ENABLE-OUT (EO) pada IC ini memungkinkan ekspansi. Misalnya, dua 74148 dapat di-cascade untuk membuat pembuat enkode prioritas 16 baris hingga empat baris.

4. PRINSIP KERJA

I0-I7 adalah 8 pilihan INPUT, bebas diisi dengan input digital Y adalah output Y bar adalah Versi NOT dari Y ABC adalah input selector. input dapat dipilih dengan mengatur kombinasi input pada ABC bilangan biner untuk A adalah 1 B adalah 2 dan C adalah 4 E adalah input yang fungsinya untuk mengatur kondisi output. Prinsip gerbang OR adalah output akan berlogika 0 jika kedua input berlogika 0 dan sebaliknya output akan berlogika 1 jika salah satu atau semua input berlogika 1.

-JIKA X0 berlogika 1 maka output Y U1 berlogika 1 kemudian masuk ke OR dimana kaki 1 berlogika 1 dan kaki 2 berlogika 0 menghasilkan output berlogika 1 sesuai dengan prinsip kerja gerbang OR. sebaliknya jika X0 berlogika 0 maka output Y U1 akan berlogika 0 (kaki 1) dan kaki 2 dalam keadaan berlogika 0 sehingga 0,0 akan mengasilkan output berlogika 0 sesuai dengan prinsip kerja gerbang OR.

-JIKA X1 berlogika 1 maka output Y U1 akan berlogika 0, untuk menghasilkan output dengan logika 1 maka kaki ABC bertindak sebagai input selektor, dimana input ABC akan dipilih mana bilangan binernya yang sesuai dengan angka pada kaki X1, disini yg diminta adalah X1 maka biner nya adalah 1 yaitu kaki A. untuk itu A berlogika 1 dan X1 berlogika 1 sehingga outputnya akan berlogika 1 kemudian masuk ke gerbang OR dimana kaki 2 berlogika 0 sehingga (1,0) akan menghasilkan output dengan logika 1

-JIKA X2 berlogika 1 maka outputnya akan berlogika 0, untuk membuat outputnya aktif(berlogika 1) maka diperlukan input selector pada ABC yang binernya sama, dima X2 binnernya 2, yg binnernya 2 adalah B, Maka kaki B inputnya berlogika 1 dan kaki X2 berlogika 1 menghasilkan output berlogika 1, kemudian masuk ke gerbang OR dimana kaki 2 dari gerbang OR berlogika 0 maka outputnya akan berlogika 1

-Untuk X3-X7 prinsipnya sama dengan X0-X2, dimana untuk membuat outputnya berlogika 1 maka diperlukan kaki ABC yang binernya sama dengan nilai kaki pada IC 74HC151 Sebagai kombinasi untuk mengaktifkan Kaki IC 74HC151 sehingga menghasilkan output dengan logika 1

-kemudian untuk U2 (Multiplexser) prinsipnya sama dengan U1, bedanya pada U2 terdapat inverter yang membuat logika pada kaki E aktif renda menjadi berlawanan dengan yg seharusnya karena inverter disini bertindak sebagai pembalik NOT sehingga output yang dihasilkan akan berkebalikan

dengan prinsip aktif rendah yaitu ketika di U1 E akan aktif jika berlogika 0 sedangkan pada u2 E akan aktif jika berlogika 1

Gambar 8.15

Ketika D0 logika 0 tidak U1 U2 dan U3 OFF, karena tidak terhubung dengan salah satu gerbang logika OR. Ini menandakan bahwa addres dari D0 adalah 0 0 0.

Ketika D1 logika 1 maka OR 3 akan aktif karena D1 terhubung dengan salah satu kaki input OR 3. Karena salah satu kaki input OR 3 berlogika 1 maka output dari OR 3 akan menjadi 1. Ini menandakan bahwa addres dari D1 adalah 1 0 0.

ketika D2 logika 1 maka OR 2 akan aktif karena D2 terhubung dengan salah satu kaki input OR 2. Karena salah satu kaki input OR 2 berlogika 1 maka output dari OR 2 akan menjadi 1. Ini menandakan bahwa addres dari D2 adalah 0 1 0.

Ketika D3 logika 1 maka OR 2 dan OR 3 akan aktif karena D3 terhubung dengan salah satu kaki input OR 2 dan OR 3. Karena salah satu kaki input OR 2 dan OR 3 berlogika 1 maka output dari OR 2 dan OR 3 akan menjadi 1. Ini menandakan bahwa addres dari D3 adalah 1 1 0.

Ketika D4 logika 1 maka OR 1 akan aktif karena D4 terhubung dengan salah satu kaki input OR 1. Karena salah satu kaki input OR 1 berlogika 1 maka output dari OR 1 akan menjadi 1. Ini menandakan bahwa addres dari D4 adalah 0 0 1.

Ketika D5 logika 1 maka OR 1 dan OR 3 akan aktif karena D5 terhubung dengan salah satu kaki input OR 1 dan OR 3. Karena salah satu kaki input OR 1 dan OR 3 berlogika 1 maka output dari OR 1 dan OR 3 akan menjadi 1. Ini menandakan bahwa addres dari D5 adalah 1 0 1.

Ketika D6 logika 1 maka OR 1 dan OR 2 akan aktif karena D6 terhubung dengan salah satu kaki input OR 1 dan OR 2. Karena salah satu kaki input OR 1 dan OR 2 berlogika 1 maka output dari OR 1 dan OR 2 akan menjadi 1. Ini menandakan bahwa addres dari D5 adalah 0 1 1.

Ketika D7 logika 1 maka OR 1, OR 2 dan OR 3 akan aktif karena D7 terhubung dengan salah satu kaki input OR 1, OR 2 dan OR 3. Karena salah satu kaki input OR 1, OR 2 dan OR 3 berlogika 1 maka output dari OR 1, OR 2 dan OR 3 akan menjadi 1. Ini menandakan bahwa addres dari D5 adalah 1 1 1.

Karena input dan output dari jenis encoder yang dipakai adalah aktif rendah maka

situasi adanya input dan output ditandakan dengan logika 0.

Bilangan biner dari

Q0 = 1

Q1 = 2

Q2 = 4

Q3 = 8

output dari encoder adalah penjumlahan angka biner sesuai dengan angka input

jika input 1 diaktifkan (logika 0) maka output dari Q0 akan berlogika 0, 1+0+0+0=1

jika input 2 diaktifkan (logika 0) maka output dari Q1 akan berlogika 0, 0+2+0+0=2

jika input 3 diaktifkan (logika 0) maka output dari Q0 dan Q1 akan berlogika 0, 1+2+0+0=3

jika input 4 diaktifkan (logika 0) maka output dari Q2 akan berlogika 0, 0+0+4+0=4

jika input 5 diaktifkan (logika 0) maka output dari Q0 dan Q2 akan berlogika 0, 1+0+4+0=5

jika input 6 diaktifkan (logika 0) maka output dari Q1 dan Q2 akan berlogika 0, 0+2+4+0=6

jika input 7 diaktifkan (logika 0) maka output dari Q0, Q1 dan Q2 akan berlogika 0, 1+2+4+0=7

jika input 8 diaktifkan (logika 0) maka output dari Q3 akan berlogika 0, 0+0+0+8=8

jika input 9 diaktifkan (logika 0) maka output dari Q0 dan Q3 akan berlogika 0, 1+0+0+8=9

Gambar 8.17

Jika D1 diaktifkan (logika 1) maka pada salah satu kaki input AND berlogika 1. Salah satu kaki AND yang lain sudah berlogika 1 yang disebabkan D2 berlogika 0 terus di inverter sehingga berlogika 1. Karena kedua kaki input AND berlogika 1 maka output dari AND adalah logika 1, sehingga pada salah satu kaki input OR 2 berlogika 1, maka output dari OR 2 adalah logika 1 pada Y.

Jika D2 diaktifkan (logika 1) maka salah satu kaki input OR 1 berlogika 1, sehingga output dari OR 1 adalah logika 1 pada X.

Jika D1 dan D2 diaktifkan (logika 1) maka salah satu kaki input OR 1 berlogika 1, sehingga output dari OR 1 adalah logika 1 pada X. Karena D2 logika 1 terus di inverter menjadi berlogika 0 pada gerbang AND, maka gerbang AND tidak aktif atau berlogika 0. Karena pada kaki input OR 2 semuanya logika 0 maka output dari gerbang OR 2 adalah berlogika 0 pada Y.

Jika D3 diaktifkan (logika 1) maka salah satu kaki input dari OR 1 dan OR 2 akan berlogika 1

sehingga gerbang OR 1 dan OR 2 outputnya menjadi logika 1 pada X dan Y

5. PROSEDUR PERCOBAAN

1. Siapkan semua alat dan bahan yang diperlukan

2. Disarankan agar membaca datasheet setiap komponen

3. Cari komonen yang diperlukan di library proteus

4. Rangkai lah rangkaian sesuai gambar

5. Atur logicstate dan nilai resistor

6. Jalankan rangkaian

6. VIDEO

7. CONTOH SOAL

Rangkaian enkoder prioritas delapan baris hingga tiga baris dengan D0 D1 D2 D3 D4 D5 D6 dan D7 sebagai jalur input data. bit keluarannya adalah A (MSB), B dan C (LSB). Bit data tingkat tinggi telah diberi prioritas lebih tinggi, dengan D7 memiliki prioritas tertinggi. Jika input dan output data aktif saat LOW, tentukan status logika bit output untuk status logika input data berikut:

(a) Semua input berada dalam status logika '0'.

(b) D1 hingga D 4 dalam status logika '1' dan D5 hingga D7 dalam status logika '0'.

(c) D7 dalam status logika '0'. Status logika dari input lainnya tidak diketahui.

Jawaban :

(a) Karena semua input berada dalam status logika '0', ini berarti bahwa semua input aktif. Karena D7 memiliki yang tertinggi prioritas dan semua input dan output aktif ketika LOW, bit output adalah A = 0, B = 0 dan C = 0.

(b) Input D5 hingga D7 adalah yang aktif. di antaranya, D7 memiliki prioritas tertinggi. Karena itu,

bit keluarannya adalah A = 0, B = 0 dan C = 0.

(c) D7 aktif. Karena D7 memiliki prioritas tertinggi, itu akan dikodekan terlepas dari status logikanya

masukan lainnya. Oleh karena itu, bit keluarannya adalah A = 0, B = 0 dan C = 0.

8. PROBLEM

1. Rancang encoder prioritas empat baris hingga dua baris dengan input dan output HIGH aktif, dengan prioritas ditetapkan ke jalur input data tingkat tinggi!

Jawaban :

Tabel kebenaran untuk encoder prioritas diberikan pada Tabel 8.10, dengan D0, D1, D2 dan D3 sebagai data input dan X dan Y sebagai output.

Ekspresi Boolean untuk dua jalur keluaran X dan Y diberikan oleh persamaan :

Gambar 8.17 menunjukkan diagram logika yang mengimplementasikan fungsi Boolean yang diberikan dalam persamaan.

Tabel 8.10

Gambar 8.17

2.

Jelaskan apakah fungsi dari kaki input A B dan C ?

Jawab : fungsinya yaitu untuk mengirimkan addres sesuai dengan angka dari kaki input X0 - X7 dari multiplexer. Jika addres yang dikirimkan salah maka tidak ada output yang muncul walaupun terdapat input. Pada kaki input A B dan C yaitu berlaku konversi bilangan biner, dimana A = 1, B = 2, C = 4. Contoh misalkan terdapat input pada kaki X6 maka addresnya adalah 1 1 0 supaya ada outputnya, dimana C = berlogika 1, B = berlogika 1, C = berlogika 0. Sehingga 4+2+0=6, maka addresnya adalah 6 sehingga outputnya akan berlogika 1.

3. Dengan gambar pada no 1, apakah kedua multiplexer bisa aktif bersamaan ? jelaskan !

Jawab : TIDAK, karena pada input kaki E adalah aktif rendah, jika berlogika 0 maka multiplexer akan aktif, jika berlogika 1 maka multiplexer tidak aktif. Pada logicstate yang dihubungkan dengan kaki input E, pada multiplexer 1 jika berlogika 0 maka ON, sedangkaan ketika logika 1 maka U1 OFF. Sedangkan pada multiplexer 2, terdapat inverter dimana jika inputnya logika 0 maka outputnya berlogika 1, dan begitupun sebaliknya. Sehingga kedua multiplexer tidak bisa aktif secara bersamaan.

9. PILIHAN GANDA

1.

Input apa saja yang harus aktif supaya output yang berlogika 1 adalah A dan C ?

a. D0

b.D7

c.D6

d. D5

Jawaban : d

2.

Input apa saja yang harus aktif supaya output yang berlogika 0 adalah Q0 dan Q4 ?

a. Kaki input 9

b. Kaki input 2 dan 7

c. Kaki input 6

d. Kaki input 2 dan 4

Jawaban : a

10. LINK DOWNLOAD

Tidak ada komentar:

Posting Komentar